# PCB Design Sequence – Part 1

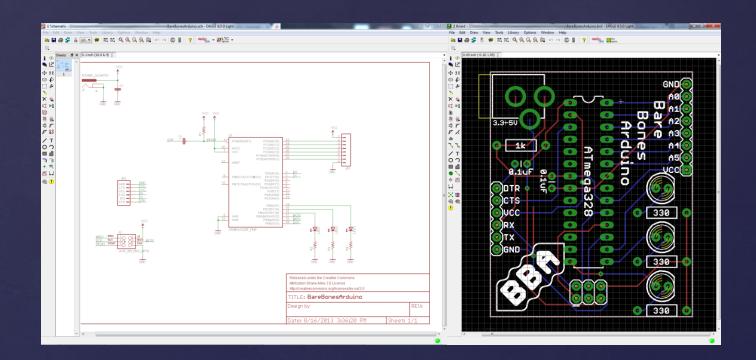

ELTN 115 Tom Thoen – Teacher / Student / Hobbyist / Inventor So far we have covered the steps for using Eagle to create schematics and the basics of board layouts. Let's look at the detailed steps of designing a PCB

## Assumptions before designing a PCB:

- You are starting with a valid (functional / correct / tested) schematic

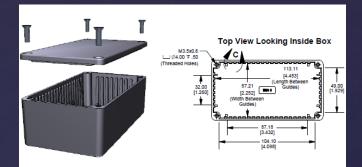

- You have an idea about the size of the enclosure you will be using.

The first steps are:

- 1. Determining the dimensions of all the components

- 2. Selecting the components from the libraries

- 3. Making all net connections

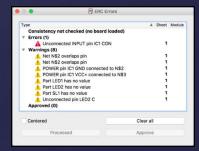

- 4. Running the ERC to check for any errors

<u>*However*</u> – even if the schematic is correct you can still make mistakes in creating the schematic in Eagle!  $\begin{array}{c|c} & L max \\ & & \downarrow \\ 0.5 max \\ & & \downarrow \\ &$

This means that once your schematic is completed it still needs to be validated / tested

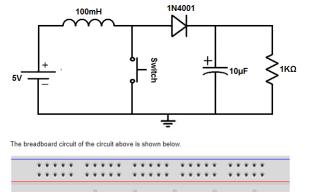

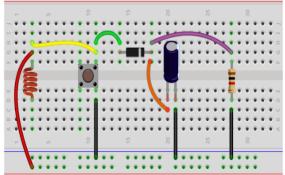

## Validation through breadboarding

Breadboarding based on your CAD (Eagle) schematic is an important step in validating the design.

If this is NOT done, it is easy to miss a mistake that ends up all the way to the completed PCB itself.

If any mistakes are found, they need to be corrected *before* moving forward. This can include wiring errors, incorrect component values, etc.

#### Board Layout:

- We usually start with the dimensions of the board based on the enclosure size

- Next, mounting holes and other physical features are created.

Once these have been determined:

- 1. Layout the components

- 3. Route the board

- 4. Add / move silkscreen text

<u>*However*</u> – even if the schematic is correct you can still make mistakes in creating the schematic in Eagle!

This means that once your schematic is completed it still needs to be validated / tested

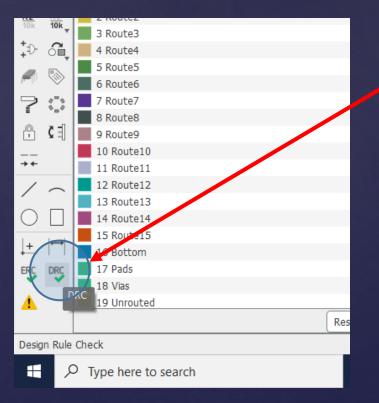

### DRC: Design rule check

- The design rule check is used to evaluate if trace widths and spaces are valid

- This is located in the Board program vertical tool bar called DRC.

## DRC: Design rule check

• There are multiple criteria that can be selected. We are usually most interested in Clearance, Distance and Sizes

| 🖷 DR        | DRC (default)                                                                                                                                                                                                                          |           |          |       |              |        |        |            |         |                  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|-------|--------------|--------|--------|------------|---------|------------------|--|--|

| File        | Layers                                                                                                                                                                                                                                 | Clearance | Distance | Sizes | Annular Ring | Shapes | Supply | Masks      | Misc    |                  |  |  |

| EAG         | LE Design                                                                                                                                                                                                                              | Rules     |          |       |              |        |        |            |         |                  |  |  |

| The<br>requ | The default Design Rules have been set to cover a wide range of applications. Your particular design may have different requirements, so please make the necessary adjustments and save your customized design rules under a new name. |           |          |       |              |        |        |            |         |                  |  |  |

|             |                                                                                                                                                                                                                                        |           |          |       |              |        |        |            |         |                  |  |  |

|             |                                                                                                                                                                                                                                        |           |          |       |              |        |        |            |         |                  |  |  |

|             |                                                                                                                                                                                                                                        |           |          |       |              |        |        |            |         |                  |  |  |

|             |                                                                                                                                                                                                                                        |           |          |       |              |        |        |            |         |                  |  |  |

|             |                                                                                                                                                                                                                                        |           |          |       |              |        |        |            |         |                  |  |  |

|             |                                                                                                                                                                                                                                        |           |          |       |              |        |        |            |         |                  |  |  |

|             |                                                                                                                                                                                                                                        |           |          |       |              |        |        |            |         |                  |  |  |

|             |                                                                                                                                                                                                                                        |           |          |       |              |        |        |            |         |                  |  |  |

|             |                                                                                                                                                                                                                                        |           |          |       |              |        |        |            |         |                  |  |  |

|             |                                                                                                                                                                                                                                        |           |          |       |              |        |        |            |         | Edit Description |  |  |

|             |                                                                                                                                                                                                                                        |           |          |       |              |        |        | a into cur | ant cot | tings Lond       |  |  |

|             | merge into current settings Load Save as                                                                                                                                                                                               |           |          |       |              |        |        |            |         |                  |  |  |

|             |                                                                                                                                                                                                                                        |           |          |       |              | [      | Check  | S          | elect   | Cancel Apply     |  |  |

## DRC: Design rule check

- For the most part we can use the default settings without any issues.

- However, in more complex designs we might need to change these settings if there are lots of traces and vias.

- For example, if we need to make sure the space between traces and vias can't be closer than 10 mils, we can change this filter when running the DRC

| 9 DRC | C (default) |              |             |            |                                                                          |            |            |          |      |      |   |

|-------|-------------|--------------|-------------|------------|--------------------------------------------------------------------------|------------|------------|----------|------|------|---|

| File  | Layers      | Clearance    | Distance    | Sizes      | Annular Ring                                                             | Shapes     | Supply     | Masks    | Misc |      |   |

|       |             |              |             |            |                                                                          |            | Differe    | ent Sign | als  |      |   |

|       |             |              |             |            | Wire                                                                     |            |            |          |      |      |   |

|       |             |              | Wi          | ire 6m     | li                                                                       |            |            | Pad      |      | 1    |   |

|       |             |              | Pa          | d 6m       | il                                                                       |            | 6mil       |          |      | Via  | 1 |

|       |             |              | Via         | a 10       | mil                                                                      |            | 6mil       |          |      | 6mil |   |

|       |             |              |             |            |                                                                          |            | Sam        | e Signak | 5    |      |   |

|       |             | ▶   ◄        |             |            | Smd                                                                      |            |            | Pad      |      | Via  | 1 |

| ļ     |             |              | Sm          | nd 6m      |                                                                          |            | 6mil       |          |      | 6mil |   |

| The s | Same Sig    | nals check d | oes not app | ly if an 3 | a does not apply<br><i>Sind</i> and <i>Sind/Pa</i><br>s to 0 disables th | dare in th | e same foo | otprint. |      |      |   |

|       |             |              |             |            |                                                                          |            |            |          |      |      |   |

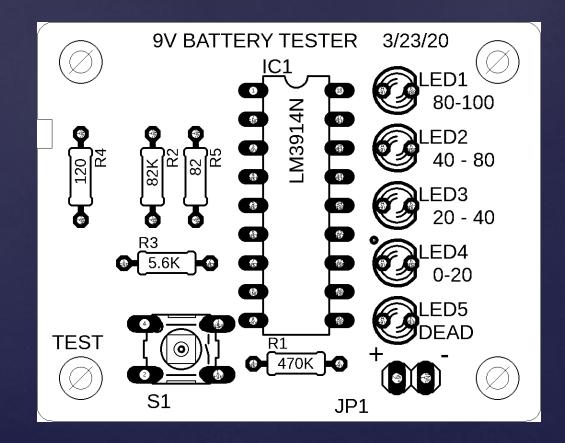

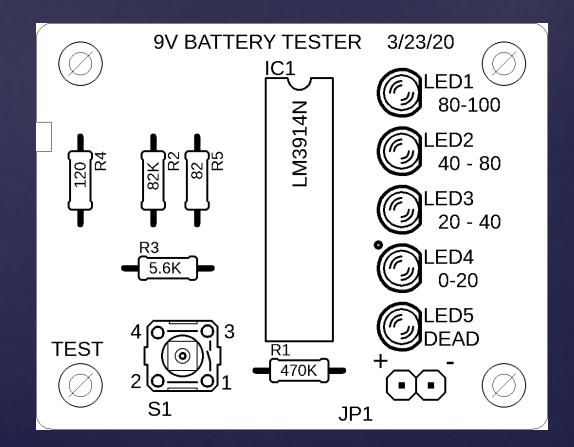

#### Physical verification of components

- In order to make sure that the proper component packages are selected, a 1:1 print is made and then compared to the actual physical components.

- Note if the components have not been received yet, this step is done later. However, it must be done before ordering the board!

#### Assembly print

• The assembly print is basically an image of the board (without traces) that helps the manufacturer know where parts are located. It is used with the BOM to assemble the board.

#### Procurement

- Before the board is ordered the components are ordered.

- Two main reasons for the sequence:

- 1. Often the lead time for a PCB is longer than the component lead time.

- 2. It is important to validate the size of the components in case changes need to be made to the design.

### CAM Processing

- The next step is creating the CAM files. We will go into detail on this in the following week.

- The general idea is that the board file data needs to be converted into files that can be used to manufacture the board. These include files for the traces, pads, drill sizes, silkscreen etc.

## Final steps

The final steps are:

- 1. Submit files to Board house

- 2. Solder components

- 3. Test / validate

- 4. Put in enclosure

- 5. Final test